Regular Article

# Design of a Configurable 4-Channel Analog Front-End for EEG Signal Acquisition on 180nm CMOS Process

# Duc-Hung Le<sup>1</sup>, The-Hung Pham<sup>1</sup>, Cong-Kha Pham<sup>2</sup>

- <sup>1</sup> Faculty of Electronics and Telecommunications, The University of Science Vietnam National University Ho Chi Minh City, Ho Chi Minh City, Vietnam

- <sup>2</sup> The University of Electro-Communicatios, Tokyo, Japan

Correspondence: Duc-Hung Le, ldhung@hcmus.edu.vn

Communication: received 09 November 2023, revised 22 December 2023, accepted 26 December 2023

Online publication: 03 January 2024, Digital Object Identifier: 10.21553/rev-jec.339

The associate editor coordinating the review of this article and recommending it for publication was Prof. Hoang Van Phuc.

Abstract– In this work, a 4-channel Analog Front-End (AFE) circuit has been proposed for EEG signal recording. For EEG recording systems, the AFE may handle a wide range of sensor inputs with high input impedance, adjustable gain, low noise, and wide bandwidth. The buffer or current-to-voltage converter block (BCV), which can be set to operate as a buffer or a current-to-voltage converter circuit, is positioned between the electrode and the main amplifier stages of the AFE to achieve high input impedance and work with sensor signal types. A chopper capacitively-coupled instrumentation amplifier (CCIA) is positioned after the BCV as the main amplifier stage of the AFE to reduce input-referred noise and balance the impedance of the overall AFE system. A programmable gain amplifier (PGA) is the third stage of the AFE that allows the overall gain of the AFE to be adjusted. The suggested AFE operates in a wide frequency range of 0.5 Hz to 2 kHz with a high input impedance bigger than 2  $T\Omega$ , and it is constructed and simulated using a 180nm CMOS process. With the lowest 100 dB CMRR and low input-referred noise of 1.8  $\mu$ Vrms, the AFE can achieve low noise efficiency. The design incorporates new features such as the BCV to enhance input variety, and the IRN and CMRR coefficients exhibit notable enhancements in comparison to prior research. EEG signals can be acquired with this AFE system, which is very useful for detecting epilepsy and seizures.

Keywords- Analog front-end, EEG signal acquisition, low noise, high input impedance, 4-channel, 180nm CMOS process.

# 1 Introduction

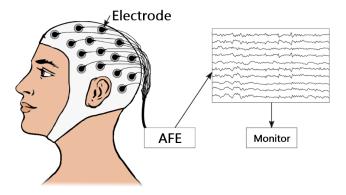

Currently, integrated circuit research and applications in the biomedical field are receiving a lot of attention. The development of CMOS technology and analog design methodologies has contributed to the efficiency and necessity of biomedical signal acquisition, particularly for EEG signals. The purpose of this work is to develop a 4-channel configurable Analog Front-End (AFE) circuit that can receive and preprocess Electroencephalogram (EEG) signals from a variety of current and voltage sensors with extremely small voltage or current amplitudes. To make pre-processing easier, the EEG signal sources from the electrodes in Figure 1 will be enhanced. An electrophysiological technique called EEG is used to record electrical activity in the brain. This sort of signal has been widely used in the medical industry, particularly in the field of neurology [1-3]. The EEG signal has a very low frequency range (0.5-100 Hz) and an average amplitude (3-100 µV). Furthermore, it is made up of multiple subband signal components with the following operating frequencies: Delta ( $\delta$ : 0.5-4 Hz), Theta ( $\theta$ : 4-7 Hz), Alpha ( $\alpha$ : 8-12 Hz), Beta ( $\beta$ : 13-30 Hz), and Gamma  $(\gamma: 30-100 \text{ Hz})$  [4–7]. Additionally, the impedance at the sensor's output is crucial in boosting the EEG signal's amplitude and reducing noise on the transmission path. It emerges between the skin and the electrode (wet or

Figure 1. EEG signal measurement with electrodes.

dry). The authors of research [8] reported that the sensor's output impedance was quite high within the EEG signal's bandwidth. The impedance may vary from 87 K $\Omega$ -1 M $\Omega$ , and at 1 Hz, it may even exceed 1 G $\Omega$ .

The acquisition of brain signals has emerged as a potential therapy for brain illnesses such as epilepsy and convulsions. Feedback stimulation is required for the effective treatment of brain illnesses. By employing signal processing techniques, the brain's EEG signals are obtained and processed in this therapy procedure to rewrite the stimulation waveform. The concept is derived from earlier studies on the architecture of AFEs with one or more input channels. The signal from the

EEG sensor, which contained a lot of noise, was amplified to different levels by the AFE design in [9] using a Low Noise Amplifier block (LNA) and a Programmable Gain Amplifier block (PGA) to make it visible. Thermal noise and flicker noise are two types of common noise detected in the recording of EEG signals at low frequencies. They commonly occur in circuits without filter components. In addition, another study [10] showed how the AFE's structure functions over an enormous frequency range of 0.1 Hz to 10 kHz when paired with the Analog-to-Digital Converter (ADC) at the back. Similarly, this approach demonstrated the adaptability of signal analysis for humans and computers. A lownoise design with tiny EEG signal amplitudes ( $\leq$ 10  $\mu$ V) was suggested by the very significant input-referred noise (IRN) value of 2.68 µVrms from 0.1 Hz to 10 kHz. Numerous applications, such as brain-computer interfaces (BCIs) and the prediction of epileptic seizures, showed success with this approach.

Based on previous research, the authors conclude that the design of these AFE circuits primarily recorded EEG data at the voltage-type sensor output and that their ability to suppress low-frequency noise is not excellent. In fact, electronic sensors can provide many type of output signals including voltage, current, capacitance, resistance, and so on [11, 12]. The AFE system, on the other hand, only handles one or two types of sensor output signals. As a result, a Buffer or Current-To-Voltage Converter (BCV) is needed to setup the input, which comprises voltage type or current type. This research developed a 4-channel AFE system from our paper presented at the conference ATC 2023 that can record EEG signals from a variety of brain electrodes. The main contributions of the proposed AFE circuit consist of low noise, high input impedance, flicker noise efficiency, configurable input signal type, and configurable gain levels.

The remaining part of the paper's structure is as follows: The operational concept and architecture of the circuit are discussed in Section 2. The experimental results are presented in Section 3. Section 4 brings the paper to a conclusion.

# 2 CIRCUIT ARCHITECTURE

#### 2.1 Architecture Overview of 1-Channel AFE

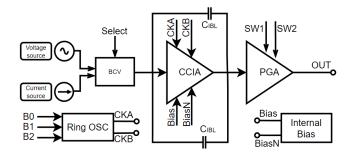

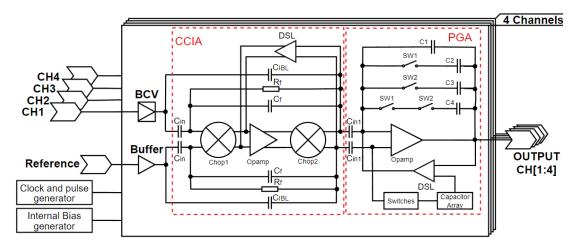

The proposed 1-channel AFE circuit, depicted in Figure 2, consists of the following blocks:

- BCV (Buffer or Current-to-Voltage Converter).

- CCIA (Coupled-Capacitive Instrument Amplifier).

- PGA (Programmable Gain Amplifier).

- Supplementary blocks: Ring Oscillator, Internal bias.

As seen in Figure 2, the three major circuits that make up the 1-channel AFE system are the BCV, CCIA, and PGA. This circuit's input signal, regardless of its voltage or current type, passes through the BCV circuit. The BCV's output then keeps going across the CCIA and PGA. The PGA's output will be connected to the AFE system's final output. As a result of the BCV circuit's

Figure 2. Block diagram of 1-channel AFE.

increased input impedance, the signal passes through the CCIA circuit, which reduces noise and amplifies the incredibly weak input signal. The output signal from the CCIA circuit will be forwarded to the PGA circuit in order to boost the amplitude of the input signal. A pair of  $C_{IBL}$  capacitors are located at the CCIA's output feedback into the input to enhance the input impedance. This approach also reduces the effect of noise at the sensor's output. Two changeable pins (SW) on the PGA circuit will help the amplitude of the output signal boost with various gain levels.

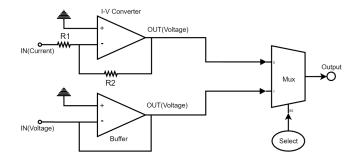

#### 2.2 Buffer or Current-to-Voltage Converter (BCV)

The authors established the BCV circuit architecture to be compatible with various kinds of EEG sensors (current or voltage sensors). This circuit can select amongst input signals by setting a "Select" bit high  $(1\ V)$  or low  $(0\ V)$ . The circuit is built as illustrated in Figure 3.

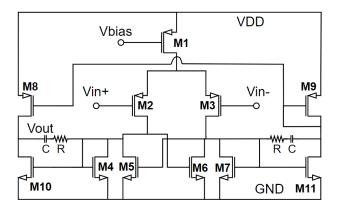

The brain tissue and electrode interaction causes a large impedance mismatch at the AFE's input when the EEG signal is being measured at the sensors or electrodes [13–16]. In order to improve EEG signal acquisition, the input impedance of AFE may occasionally be as high as 1 G $\Omega$  [17–20]. As a result, managing the electrode-tissue impedance mismatch requires a high input impedance (more than 1 G $\Omega$ ) for the BCV at the first AFE stage. To guarantee the input impedance magnitude, the BCV circuit architecture includes active components like Op-Amp. The low amplitude signal that crosses the CCIA and PGA blocks is amplified as effectively as possible based on this method. The BCV circuit's architecture necessitates the use of multiple 2stage Op-Amps as it will be driving large loads (like the PGA and CCIA) behind it. Figure 4 displays the 2stage Op-Amp schematic. The multiplexer (MUX) 2-1 circuit will be used to select the signal that corresponds to the current or voltage source of the sensor as the BCV input. Table I presents this selection.

Table I Function of the BCV as Buffer or I-V Converter

| Select Pin | Input          | Types of Circuit |  |  |

|------------|----------------|------------------|--|--|

| High (1 V) | Voltage source | Buffer           |  |  |

| Low (0 V)  | Current source | I-V Converter    |  |  |

Figure 3. Buffer or Current-to-Voltage Converter Block.

Figure 4. The schematic of the 2-stage Op-Amp circuit.

# 2.3 Capacitively-Coupled Instrumentation Amplifier (CCIA)

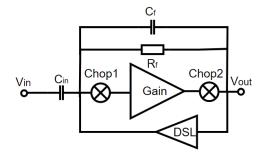

Biomedical electronics circuits usually use the CCIA circuit because of its low noise and ability to remove common mode DC input. Flicker noise is a crucial consideration for circuits operating at low frequencies, especially biomedical electronic circuits [21, 22]. Flicker noise in semiconductors is presented at both the substrate layer and the oxide gate [23]. Currents may be randomly discharged as flicker noise after being locked in an energy state while passing through this layer. Op-Amp circuits that are placed before the CCIA block, like the BCV block, may experience this flicker noise. As a result, the approach is to modulate the EEG signal from low to high frequency using circuit Chopper 1. After that, the high-frequency signal is amplified to a particular amount. Finally, before delivering the signal to the CCIA output, Chopper 2 demodulates the high-frequency and larger amplitude signal to a lowfrequency signal. In addition, a high-pass filter circuit is built by connecting the resistor  $R_f$  and capacitor  $C_f$  to reduce undesirable low-frequency noise [24–26]. Moreover, the DSL (DC servo loop) block is used to reduce the DC offset at the sensor, supporting the CCIA circuit in avoiding the saturation voltage threshold at the output [27, 28]. Figure 5 depicts the CCIA circuit.

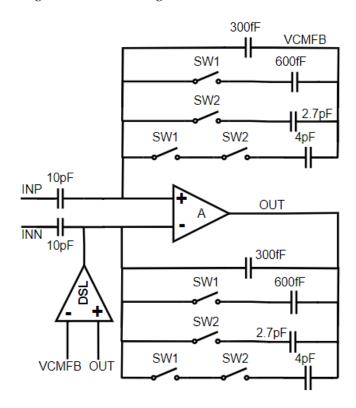

#### 2.4 Programable Gain Amplifier (PGA)

Gain control is a characteristic of PGA circuit design [29–31]. This will allow the AFE circuit to alter the gain factor, allowing users to amplify input signals of varying amplitudes. Using an Op-Amp circuit and capacitor arrays, the PGA circuit amplifies the signal

Figure 5. The CCIA circuit schematic.

from the previous CCIA block. Two switches (SW1 and SW2) control the equivalent feedback capacitance. The PGA circuit generates an adjustable gain based on the configuration of the two switches. The PGA circuit diagram is shown in Figure 6.

Figure 6. The PGA circuit schematic.

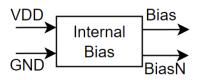

#### 2.5 Internal Bias

The term "Bias" relates to the selection of basic operating conditions for an electrical circuit. Current and voltage are two examples of operational conditions. Internal current and voltage must be stable in order for a circuit to work effectively. The current and voltage readings are now known as "Bias" values.

The Internal Bias block is depicted in Figure 7. In this design, the Internal Bias block will create two stable voltage levels to supply the circuits at lower levels within. The fundamental reason for bias voltage is that the AFE circuit includes a variety of amplifiers that perform well with a specific bias.

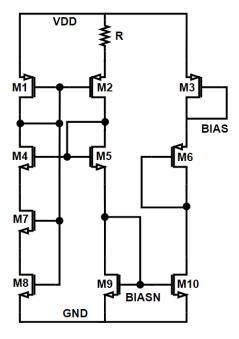

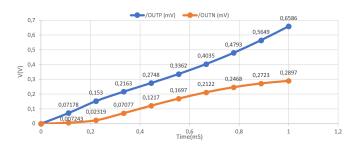

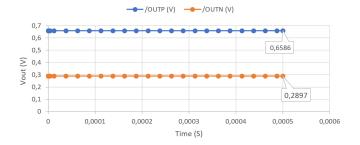

Figure 8 depicts the Internal Bias schematic for this study. The circuit generates Bias voltage = 658 mV and

Figure 7. Block diagram of Internal Bias.

Figure 8. Internal Bias circuit schematic.

BiasN voltage = 286 mV with supply power: VDD = 1 V and GND = 0 V. To obtain the required voltage levels, the authors use a voltage divider structure through resistors or the diode-connected load structure. When a certain resistor value cannot be designed due to layout constraints, the diode-connected load structure is used.

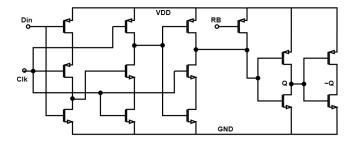

# 2.6 Ring Oscillator

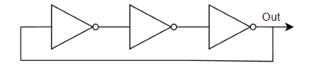

The Ring Oscillator's function is to produce a clock pulse, which is a periodic electrical signal. The signal that is generated will have a square waveform. Simple ring oscillator structures only require an odd number of serial inverters; the ring oscillator circuit in Figure 9 has three odd-numbered inverter circuits. Three bits–B0, B1, and B2–control the Ring Oscillator's output signal frequency.

Figure 9. Odd-Inverter's Ring Oscillator circuit schematic.

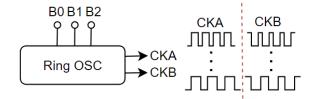

The circuit comprises three bits (B0, B1, B2) that control the output frequency of the Ring Oscillator, as shown in Figure 10. These output signals of different frequency values will be fed into the two Chopper circuits of the CCIA block described above. The Ring Os-

Figure 10. The output signal frequency of the Ring Oscillator.

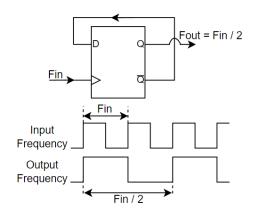

cillator block will be made up of three delay-generating blocks (Delay Cell) connected in series to create the appropriate frequency difference. Furthermore, the circuit contains two Flip-Flop D (FFD) components that divide the frequency by four. Figure 11 depicts a frequency divider circuit employing FFD with the desired frequency value of several tens of thousands of Hz at the output. After passing through two FFDs, the signal will be routed through two inverter arrays to consolidate its ability to drive loads. The first array is the CKB pin, which is subsequently connected to the CKA pin via the second array. In actuality, the CKA and CKB output signals have the same frequency but phase inversion.

Figure 11. Flip-Flop D circuit for frequency division.

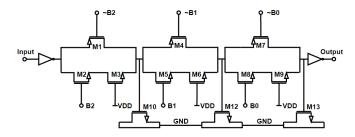

Figure 12. Delay cell circuit schematic.

The Delay Cell block is made up of two inverters that are inserted at the start and end of a Voltage-controlled Oscillator (VCO) circuit to generate a particular delay. Furthermore, the VCO block has three stages that establish the delay in the time domain. As shown in Figure 12, each stage is a Transmission Gate (TG), which includes two NMOS and one PMOS transistor connected in parallel. Because TG is controlled by a couple of external voltages, it can change the delay value based on the capacitances behind it [32]. Figure 13 depicts the FFD schematic. Figure 14 shows

the whole structure of the Ring Oscillator circuit, which comprises circuits such as the Delay Cell, Flip-Flop D, and Inverter.

Figure 13. Flip-Flop D circuit schematic.

Figure 14. The structure of the Ring Oscillator circuit.

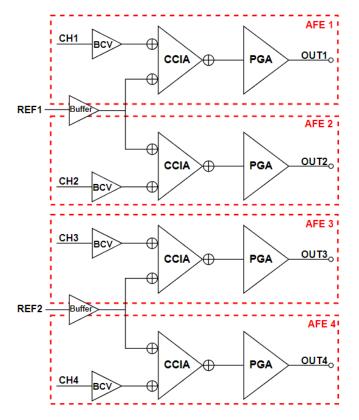

#### 2.7 Design of 4-Channel Analog Front-End Circuit

The proposed 4-channel Analog Front-end (AFE) system is shown in Figure 15. The design includes 4 blocks of a 1-channel AFE circuit. We utilize two reference buffers as the negative input, so each of them shares with two 1-channel AFE circuits in order to accomplish the goal of saving area and resources as illustrated in Figure 16. Additionally, to reduce the system's overall power consumption, the 4-channel AFE circuit employs the same Internal Bias and Ring Oscillator circuit. The addition of the BCV block makes it simple to select an input from a variety of sensor output signal types (current and voltage). In order to prevent the effects of the impedance mismatch of the AFE system caused by brain tissue and electrodes, BCV can be configured as a buffer or a current-to-voltage converter using two Op-Amps to achieve high input impedance. A good way to both reduce flicker noise and stimulate input signal is to use the PGA and CCIA together. For the purpose of recording EEG signals, the CCIA functions as the first-stage amplifier. The input signal is low noise with the CCIA, and the DC offset voltage that directly affects the signal from the sensor is completely eliminated. The CMRR and IRN factors are thus significantly reinforced. Meanwhile, the PGA acts as the second-stage amplifier, increasing the overall gain of the AFE with four different levels. The amplitude of the output signal can be changed by controlling the expected gain values with two PGA circuit switches. Based on the 180nm CMOS process, the structure of a configurable low-noise 4-channel AFE was designed.

#### 3 Experimental Results

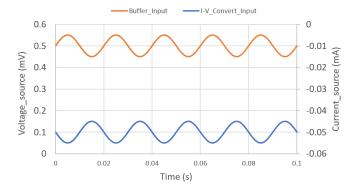

#### 3.1 Buffer or Current-to-Voltage Converter Circuit

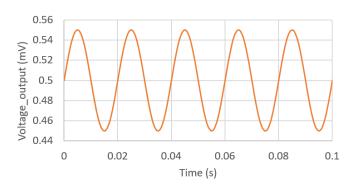

As previously stated, the BCV circuit is made up of two basic blocks: a current-to-voltage converter and a buffer. In order to test the BCV circuit, we need to provide an input signal with an amplitude of 50  $\mu V$  for voltage and -5  $\mu A$  for current, respectively, with the frequency of 1 kHz in the time domain. Next, with the goal to assess how well the circuit is working, we will look at the signal at the BCV circuit's output. The current and voltage sources that will be fed into the BCV circuit are depicted in Figure 17. The output waveform displayed in Figure 18 of the BCV further ensures that the type of signal after conversion is voltage with an estimated amplitude of 50  $\mu V$ .

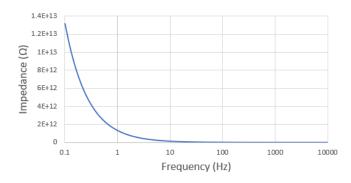

To evaluate the performance of this circuit, the AFE's input impedance is simulated. Figure 19 depicts the input impedance result. This circuit has a relatively high input impedance (>2  $T\Omega$ ), making it appropriate for the sensor impedance requirement and low-noise capability.

#### 3.2 Internal Bias

The simulation waveform based on the DC and transient simulation is shown in Figure 20 and Figure 21 with the VDD of 1 V and the VSS of 0 V as follows. According to the results of the previous two simulations, the circuit performed as expected.

## 3.3 Ring Oscillator

The above circuit generates frequencies using three bits (B2, B1, B0): 000, 001, 010, 011, 100, 101, 110, and 111 with the voltage supply of the VDD of 1 V and the VSS of 0 V. The frequency results at the CKA pin are measured at the pre-layout and post-layout simulation shown in Table II. The same frequencies are achieved at the CKB pin.

Table II

THE FREQUENCY RESULTS WITH 3-BIT SETTINGS

| Bit<br>(B2 B1 B0) | Pre-Layout<br>(kHz) | Post-Layout<br>(kHz) |

|-------------------|---------------------|----------------------|

| 000               | 28.35               | 28.17                |

| 001               | 24.8                | 24.75                |

| 010               | 21.76               | 21.79                |

| 011               | 19.61               | 19.61                |

| 100               | 18.27               | 18.25                |

| 101               | 16.73               | 16.64                |

| 110               | 15.23               | 15.29                |

| 111               | 14.14               | 13.99                |

#### 3.4 The Proposed AFE Circuit

The 4-channel AFE circuit is built from four 1-channel AFE circuits. As a result, the simulation will be run on each 1-channel AFE circuit. The BCV, CCIA, and PGA blocks make up the 1-channel AFE circuit. The input signal to the circuit can be either a current or a voltage

Figure 15. The architecture of the proposed configurable 4-channel AFE.

Figure 16. Block diagram of the 4-channel AFE sharing reference input signals.

source. The user has to control the "Select" bit of the BCV block, as shown in Table I, to select the type of input signal. The signal is then processed by the CCIA circuit, which filters noise and amplifies it to the desired level. By passing it through the PGA circuit, the signal is amplified once more. The two switches (SW1 and SW2) are used to configure the gain in the PGA circuit. The AFE circuit's output port corresponds to the PGA circuit's output port. The overall gain of the 1-channel AFE circuit can be calculated by measuring the value at this pin.

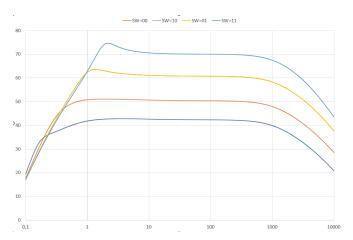

3.4.1 AC Simulation: The gain simulated at the AFE's output ranges from 42 dB to 70 dB for an input waveform with Magnitude = 1 V, as shown in

Figure 17. The current and voltage input signals of the BCV circuit.

Figure 18. The output voltage signal of the BCV circuit.

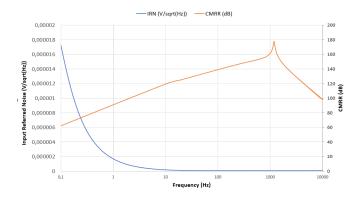

Figure 22. Furthermore, the input-referred noise (IRN) and common-mode ratio rejection (CMRR) values are measured to evaluate the performance of the circuit depicted in Figure 23. The technique and approach for creating the testbench for evaluating the circuit using IRN and CMRR values are described in [33] and [34], respectively.

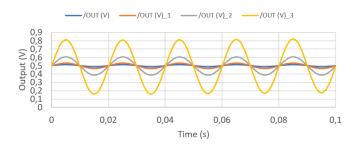

3.4.2 Transient Simulation: The input signal parameters include an amplitude of 50  $\mu V$  and a frequency of 1 kHz. Figure 24 shows the output waveform produced by this input signal. SW1 and SW2 are configured as follows: 00, 10, 01, 11. Each bit pair will correspond to a different output amplitude. The circuit operates properly between 0.5 Hz and 2 kHz.

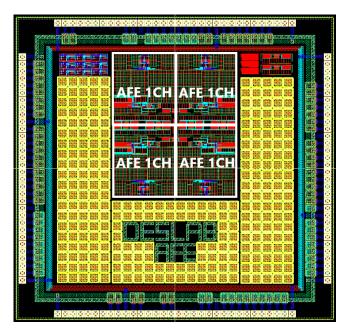

The layout for the 4-channel AFE circuit based on the

Figure 19. The input impedance of Op-Amp.

Figure 20. The DC simulation result of Internal Bias circuit.

Figure 21. The transient simulation result of Internal Bias circuit.

Figure 22. The gain results of each channel of the AFE circuit with AC simulation.

1-channel AFE is also depicted in Figure 25. The assessment results for the 4-channel AFE circuit are displayed in Table III in terms of gain and bandwidth factors.

Each pair of control bits will have different gain coefficients and operating frequency ranges, as shown in Table III. The gain will increase or decrease according to how the bit pair's values are set. The results of the proposed 4-channel AFE circuit are displayed in

Figure 23. Input-referred noise and CMRR results with AC simulation

Figure 24. The output amplified signals of the AFE corresponding to SW1-SW2 configuration.

Figure 25. The full-chip layout of the 4-channel AFE on 180nm CMOS process.

$\label{thm:continuous} \text{Table III} \\ \text{Bandwidth and Gain of the 4-Channel AFE Circuit} \\$

| Bits (SW1 SW2) | Bandwidth                                       | Gain(dB) |  |

|----------------|-------------------------------------------------|----------|--|

| 00             | $0.5~\mathrm{Hz}  ightarrow 2~\mathrm{kHz}$     | 42.06    |  |

| 10             | $0.65~\mathrm{Hz}  ightarrow 1.98~\mathrm{kHz}$ | 50.15    |  |

| 01             | $1.2~\mathrm{Hz} \rightarrow 1.95~\mathrm{kHz}$ | 60.5     |  |

| 11             | $2.3~\mathrm{Hz} \rightarrow 1.8~\mathrm{kHz}$  | 70       |  |

| Table IV           |

|--------------------|

| COMPARISON RESULTS |

|                    | [35]        | [36]       | [37]         | [38]        | [39]         | This work    |

|--------------------|-------------|------------|--------------|-------------|--------------|--------------|

| Supply Voltage (V) | 0.8         | 1.2        | 1.8          | 1.2         | 1.8          | 1            |

| Gain (dB)          | 60          | 45.2-71    | 35.04        | 26          | 52-80        | 42-70        |

| Bandwidth          | 0.9-320 Hz  | 1 Hz-7 kHz | 1 Hz-9.3 kHz | 0.1-200 Hz  | 0.1-100 Hz   | 0.5 Hz-2 kHz |

| CMRR (dB)          | 137         | >95        | 76           | 109.6       | >90          | 100-180      |

| IRN (μVrms)        | 1.7 @100 Hz | 2.93       | 3.2          | 1.2 @200 Hz | 0.91 @100 Hz | 1.8 @1 kHz   |

| Input Impedance    | 16-160 GΩ   | >100 MΩ    | 8 MΩ         | -           | >500 MΩ      | >2 TΩ        |

| Phase Margin (deg) | -           | -          | 170          | -           | -            | 150-160      |

| NEF                | 3.87        | 3.0        | 1.94         | -           | 5.1          | 1.96         |

| PEF                | 11.89       | 10.8       | 6.67         | -           | 47           | 3.84         |

| Process (nm)       | 180         | 130        | 180          | 180         | 180          | 180          |

Table IV, along with comparative data with other relevant research. This study has a wider frequency range (from 0.5 Hz to 2 kHz), greater input impedance (>2  $T\Omega$ ), good phase margin (150-160 deg), higher CMRR (100-180 dB), low IRN (1.8  $\mu$ Vrms at 1 kHz), the lowest NEF/PEF (1.96/3.84), and better gains (42-70 dB) when compared to other research [35–39]. This design has some limitations, including the usage of a large amount of capacitors and the fact that each channel's layout area is roughly 0.35 mm<sup>2</sup>.

## 4 Conclusion

On the 180nm CMOS process, a 4-channel AFE circuit was proposed and simulated. The following blocks are included in the circuit: BCV, CCIA, PGA, and other supported blocks such as Internal Bias and Ring Oscillator. The BCV is proposed to this AFE to configure the electrode's current or voltage input. The AFE's voltage output is suitable for rear analog blocks such as ADCs, filters, and so on. The proposed 4-channel AFE circuit also has high input impedance, low noise, a variety of input signal types, and reconfigurability. The proposed AFE has low noise efficiency with an input-referred noised (IRN) value of 1.8  $\mu V rms,\,a$  maximum CMRR of 180 dB, and a high input impedance of greater than 2  $T\Omega$ . The circuit can run between 0.5 Hz and 2 kHz to acquire an low EEG bandwidth and record neural signals more efficiently. The circuit operates with a large bandwidth, roughly 2 kHz, which can waste resources, but we have the ability to trade off the magnitude of the bandwidth to reduce the NEF, and PEF coefficients. The suggested AFE can be utilized to capture EEG signals for seizure and epilepsy detection.

#### ACKNOWLEDGMENT

This research was funded by Vietnam National University Ho Chi Minh City (VNU-HCM) under grant number DN2022-18-01.

#### REFERENCES

[1] T. Tang, W. L. Goh, L. Yao, and Y. Gao, "A 16-channel TDM analog front-end with enhanced system CMRR for

- wearable dry EEG recording," in *Proceedings of the IEEE Asian Solid-State Circuits Conference (A-SSCC)*, 2017, pp. 33–36.

- [2] S. Xu, Z. Wang, J. Sun, Z. Zhang, Z. Wu, T. Yang, G. Xue, and C. Cheng, "Using a deep recurrent neural network with EEG signal to detect Parkinson's disease," *Annals of Translational Medicine*, vol. 8, no. 14, 2020.

- of Translational Medicine, vol. 8, no. 14, 2020.

[3] N. Kulkarni and V. Bairagi, "Diagnosis of Alzheimer disease using EEG signals," International Journal of Engineering Research, vol. 3, no. 4, 2014.

- [4] Y.-S. Sung, W.-M. Chen, and C.-Y. Wu, "The design of 8-channel CMOS area-efficient low-power current-mode analog front-end amplifier for EEG signal recording," in *Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS)*, 2016, pp. 530–533.

- and Systems (ISCAS), 2016, pp. 530–533.

[5] A. Subasi and E. Ercelebi, "Classification of EEG signals using neural network and logistic regression," Computer Methods and Programs in Biomedicine, vol. 78, no. 2, pp. 87–99, 2005.

- [6] O. Kocadagli and R. Langari, "Classification of EEG signals for epileptic seizures using hybrid artificial neural networks based wavelet transforms and fuzzy relations," Expert Systems with Applications, vol. 88, pp. 419–434, 2017.

- [7] C. W. Anderson and Z. Sijercic, "Classification of EEG signals from four subjects during five mental tasks," in Proceedings of the Conference on Engineering Applications in Neural Networks (EANN'96). Turkey, 1996, pp. 407–414.

- [8] E. Habibzadeh Tonekabony Shad, M. Molinas, and T. Ytterdal, "Impedance and Noise of Passive and Active Dry EEG Electrodes: A Review," *IEEE Sensors Journal*, vol. 20, no. 24, pp. 14565–14577, 2020.

- [9] M. Awais Bin Altaf, C. Zhang, L. Radakovic, and J. Yoo, "Design of energy-efficient on-chip EEG classification and recording processors for wearable environments," in *Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS)*, 2016, pp. 1126–1129.

- [10] T. Zarifi, C.-C. Peng, and M. H. Zarifi, "Low-power amplifier for in-vivo EEG signal recording," in *Proceedings of the 1st Middle East Conference on Biomedical Engineering*, 2011, pp. 19–22.

[11] K. Sato, "Proposal of a unified sensing circuit for dif-

- [11] K. Sato, "Proposal of a unified sensing circuit for different sensor output types," Journal of the Institute of Industrial Applications Engineers, vol. 10, no. 2, pp. 39–45, 2022

- [12] M. Javaid, A. Haleem, R. P. Singh, S. Rab, and R. Suman, "Significance of sensors for industry 4.0: Roles, capabilities, and applications," *Sensors International*, vol. 2, p. 100110, 2021.

- [13] A.-M. Tautan, V. Mihajlovic, Y.-H. Chen, B. Grundlehner, J. Penders, and W. A. Serdijn, "Signal Quality in Dry Electrode EEG and the Relation to Skin-electrode Contact

Impedance Magnitude." in Proceedings of the Biodevices,

2014, pp. 12-22

[14] J.-C. Hsieh, H. Alawieh, Y. Li, F. Iwane, L. Zhao, R. Anderson, S. I. Abdullah, K. W. K. Tang, W. Wang, I. Pyatnitskiy et al., "A highly stable electrode with low electrode-skin impedance for wearable brain-computer interface," Biosensors and Bioelectronics, vol. 218, p. 114756, 2022.

[15] V. Mihajlović and B. Grundlehner, "The effect of force and electrode material on electrode-to-skin impedance," in Proceedings of the IEEE Biomedical Circuits and Systems

Conference (BioCAS). IEEE, 2012, pp. 57-60.

[16] Z. Zhao, K. Ivanov, L. Lubich, O. M. Omisore, Z. Mei, N. Fu, J. Chen, and L. Wang, "Signal quality and electrode-skin impedance evaluation in the context of wearable electroencephalographic systems," in Proceedings of the 40th Annual International Conference of the IEEE Engineering in Medicine and Biology Society (EMBC), 2018, pp. 4965–4968.

[17] H. A. Huynh, M. Zamani, M. Ronchini, H. Farkhani, and F. Moradi, "A 53GΩ@DC Input Impedance Multi-Channel Neural Recording Amplifier with 0.77 µVrms Input-Referred Noise for Deep Brain Implants," in Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), 2021, pp. 1-2.

[18] Q. Fan and K. Makinwa, "Capacitively-coupled chopper instrumentation amplifiers: An overview," in Proceedings

of the IEEE SENSORS, 2018, pp. 1-4.

[19] H. A. Huynh, M. Ronchini, A. Rashidi, M. Tohidi, H. Farkhani, and F. Moradi, "A low-noise high input impedance analog front-end design for neural recording implant," in Proceedings of the 26th IEEE International Conference on Electronics, Circuits and Systems (ICECS), 2019, pp. 887-890.

[20] J. Lee, G.-H. Lee, H. Kim, and S. Cho, "An ultra-high input impedance analog front end using self-calibrated positive feedback," *IEEE Journal of Solid-State Circuits*, vol. 53, no. 8, pp. 2252–2262, 2018.

[21] J. Zheng, W.-Ĥ. Ki, L. Hu, and C.-Y. Tsui, "Chopper capacitively coupled instrumentation amplifier capable of handling large electrode offset for biopotential recordings," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 64, no. 12, pp. 1392-1396, 2017.

- [22] T. Deguchi, R. Tanaka, S. Kawazoe, R. Fukuoka, and N. Nakano, "A Low Noise Analog Front-end Design with an N-path Filter for Dry EEG Recording," in Proceedings of the International Symposium on Intelligent Signal Processing and Communication Systems (ISPACS), 2018, pp. 523-526.

- [23] E. Simoen and C. Claeys, "On the flicker noise in sub-micron silicon MOSFETs," *Solid-State Electronics*, vol. 43, no. 5, pp. 865-882, 1999.

- [24] H. Song, Y. Park, H. Kim, and H. Ko, "Fully integrated biopotential acquisition analog front-end IC," Sensors,

- vol. 15, no. 10, pp. 25139–25156, 2015. [25] C.-C. Tu and T.-H. Lin, "Measurement and parameter characterization of pseudo-resistor based CCIA for biomedical applications," in Proceedings of the IEEE International Symposium on Bioelectronics and Bioinformatics (IEEE ISBB 2014). IEEE, 2014, pp. 1–4.

- [26] S. Lim, C. Seok, H. Kim, H. Song, and H. Ko, "A fully integrated electroencephalogram (EEG) analog front-end IC with capacitive input impedance boosting loop," in

Proceedings of the IEEE 2014 Custom Integrated Circuits Conference, 2014, pp. 1-4.

[27] C.-Y. Wu and C.-S. Ho, "An 8-channel chopper-stabilized analog front-end amplifier for EEG acquisition in 65nm CMOS," in Proceedings of the IEEE Asian Solid-State Circuits Conference (A-SSCC). IEEE, 2015, pp. 1–4. [28] X. Zhou, Q. Li, S. Kilsgaard, F. Moradi, S. L. Kappel,

and P. Kidmose, "A wearable ear-EEG recording system of the IEEE Symposium on VLSI Circuits (VLSI-Circuits), 2016, pp. 1–2.

[29] C. G. Lyden, R. S. Maurino, and D. J. Mccartney, "Programmable gain amplifier with amplifier common mode sampling system," Jul. 29 2014, uS Patent 8,791,754.

- [30] P. Zhang, P. Zhao, X. Chen, Y. Song, and Z. Zhang, "Offset Cancellation and Programmable Gain Design for Switched Capacitor Amplifier in Digital DC-DC Converter," in Proceedings of the IOP Conference Series: Earth and Environmental Science, vol. 714. IOP Publishing, 2021, p. 042053.

- [31] Z. Li, W. Fan, J. Xi, L. He, N. Xie, and K. Sun, "14-bit column readout circuits with single-to-differential PGA using intentional offset and two-step scaled-reference SAR ADC for CMOS image sensors," Analog Integrated

- Circuits and Signal Processing, vol. 96, pp. 159–174, 2018. [32] M.-L. Sheu, T.-W. Lin, and W.-H. Hsu, "Wide frequency range voltage controlled ring oscillators based on transmission gates," in Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), 2005, pp. 2731-2734 Vol. 3.

- [33] J. van der Spiegel, Brain-machine Interface: Closed-loop Bidirectional System Design. Springer, 2018.

- [34] S. Bandyopadhyay, D. Mukherjee, and R. Chatterjee, "Design of two stage CMOS operational amplifier in 180nm technology with low power and high CMRR," International Journal of Latest Trends in Engineering and Technology, vol. 11, 2014.

- [35] M. Tohidi, J. K. Madsen, M. J. R. Heck, and F. Moradi, "A low-power analog front-end neural acquisition design for seizure detection," in Proceedings of the IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC), 2016, pp. 1-6.

[36] T. Yang, J. Lu, M. S. Jahan, K. Griffin, J. Langford, and J. Holleman, "A configurable 5.9  $\mu$ w analog front-end for biosignal acquisition," in *Proceedings of the IEEE Custom* Integrated Circuits Conference (CICC), 2015, pp. 1-4.

- [37] M. Rezaei, E. Maghsoudloo, C. Bories, Y. De Koninck, and B. Gosselin, "A low-power current-reuse analog front-end for high-density neural recording implants, IEEE Transactions on Biomedical Circuits and Systems, vol. 12, no. 2, pp. 271-280, 2018.

- [38] J.-H. Hong, M.-C. Liang, M.-Y. Haung, T.-H. Tsai, Q. Fang, and S.-Y. Lee, "Analog front-end circuit with low-noise amplifier and high-pass sigma-delta modulator for an EEG or ECoG acquisition system," in Proceedings of the International Symposium on Bioelectronics and Bioinformations 2011, 2011, pp. 17-20.

- [39] J. Yoo, L. Yan, D. El-Damak, M. B. Altaf, A. Shoeb, H.-J. Yoo, and A. Chandrakasan, "An 8-channel scalable EEG acquisition SoC with fully integrated patientspecific seizure classification and recording processor," in Proceedings of the IEEE International Solid-State Circuits Conference, 2012, pp. 292-294.

Duc-Hung Le received a B.S. degree in Physics and an M.S. degree in Electronic Physics from the University of Science, VNU-HCM, in 2001 and 2005, respectively, and the Ph.D. degree in Advanced Science and Engineering from The University of Electro-Communications (UEC), Tokyo, Japan, in 2013. His research interests include FPGA design, IC design, digital signal processing, and biomedical electronics. Currently, he is with the Faculty of Electronics and Telecommunications, the University of Science, VNU-HCM, Vietnam.

The-Hung Pham received a B.S. degree in Electronics and Telecommunications from the University of Science, VNU-HCM, in 2023. His research interests include analog IC design and biomedical electronics. Currently, he is with the Faculty of Electronics and Telecommunications, the University of Science, VNU-HCM, Vietnam.

Cong-Kha Pham (IEEE Senior Member) received B.S., M.S., and Ph.D. degrees in Electronics Engineering from Sophia University, Tokyo, Japan, in 1988, 1990, and 1992, respectively. He is currently a professor with the Department of Information and Network Engineering, University of Electro-Communications (UEC), Tokyo, Japan. His research interests include hardware system design and implementation by FPGAs and integrated circuits. Recent projects include re-

search on energy harvest power supply and low-power data-centric sensor network systems utilizing them, the development of longdistance transmission and miniaturization equipment for sensor networks by low-power wireless, the super low-voltage device project, research on memory-based information detection systems, the hardware implementation of hardware systems by FPGAs and integrated circuits, etc. Professor Pham is teaching many undergraduate and postgraduate students and has received numerous awards for dissertations. The University of Electro-Communications Integrated Circuit Design Laboratory (Pham Lab) educates on the design, implementation, and evaluation of hardware systems and VLSI, aims to design "system-on-chip" by integrating various information processing hardware, and develops a high-performance computational circuit realized with a small number of elements.